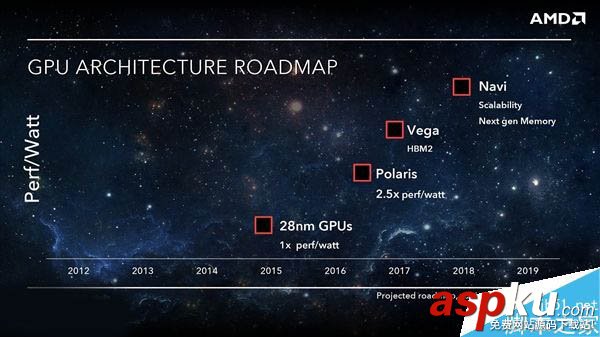

Ryzen(Zen)处理器秀了多次之后,终于轮到AMD在显卡方面的重磅新品登场亮相了,这就是全新设计的Vega(织女星)架构,定位高端,将成为AMD未来旗舰和高端显卡的基石。

AMD表示,虽然Vega、Polaris相隔不到一年,但是变化非常大,可以说是GPU图形行业五年来最大的变化,拥有革命性的四大亮点。

不过这一次,率先公开的只是Vega架构上一些整体的设计特点,更深入的技术和规格细节还要再等等。

Vega的设计理念,来源于如今的GPU架构已经不能很高效地处理最新的数据和负载需求,尤其是显存/内存架构远远跟不上计算需求的脚步。

为此,AMD Vega设计了世界上最高效、最灵活的GPU显存/内存架构,不像以往那样暴力提升显存频率或位宽来获得更大带宽,而是改变了GPU对于数据的传输处理方式。

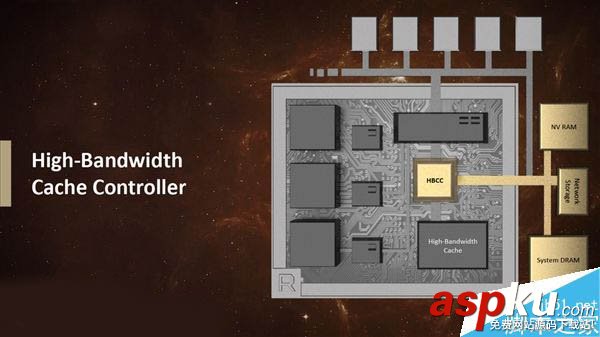

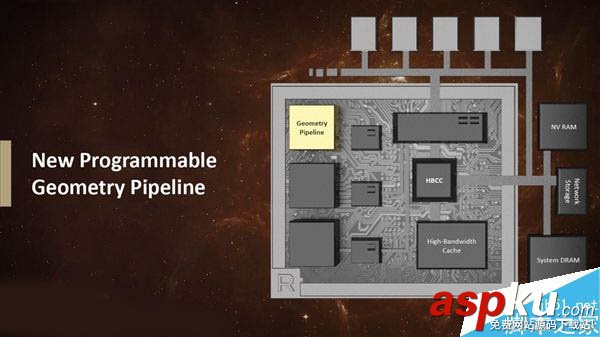

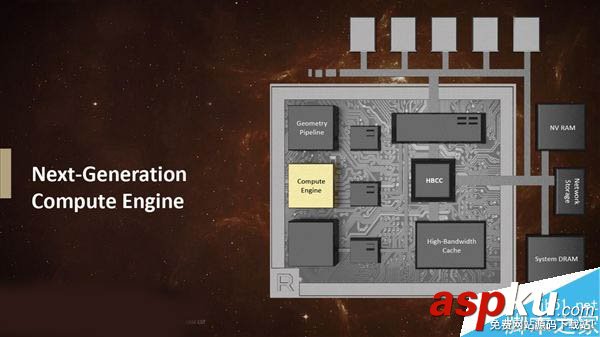

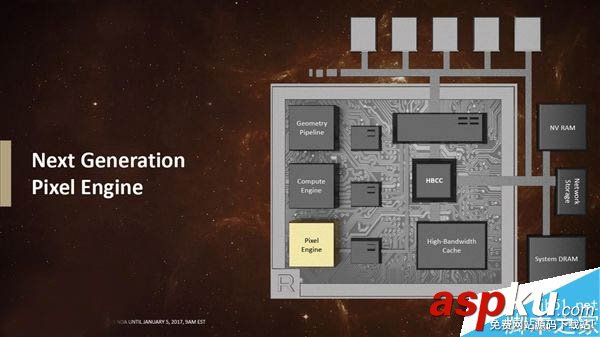

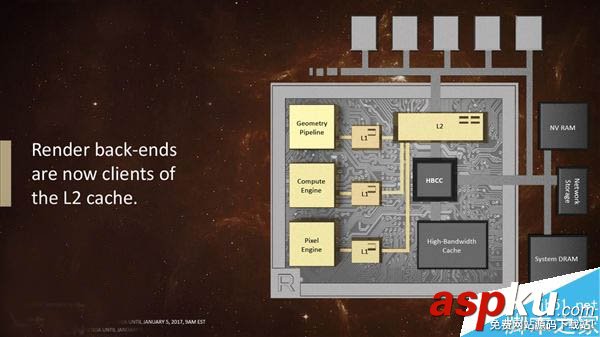

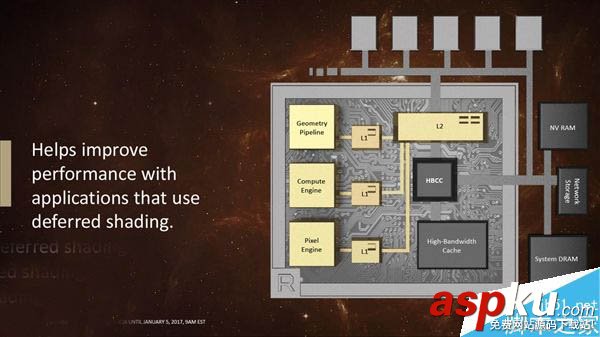

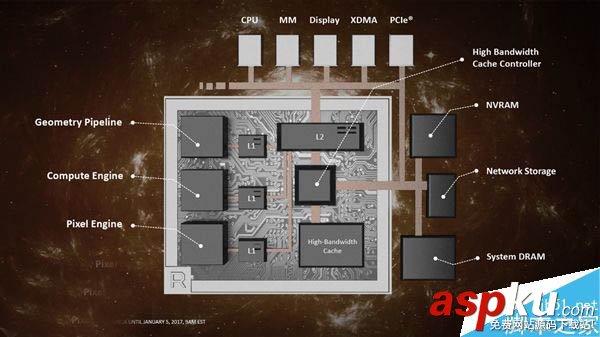

注意,图中的芯片和线路布局只是示意性的,不代表实际芯片的样子。

首先是高带宽缓存(HBC),主要就是用上了第二代高带宽显存HBM2,单位带宽是第一代的2倍达到2Gbps/pin,堆叠容量则是8倍达到8GB,同样和GPU整合在一块基板上(当然互联层做了升级),占用面积相比GDDR5小了超过50%。

Vega还特意设计了高带宽缓存控制器(HBCC),但不仅仅是管理HBM2,还负责沟通系统内存、非易失性存储(NVRAM)、网络存储。

HBCC的最大虚拟寻址空间高达512TB,可以有效管理超大数据集,AMD称之为适应性精细调节数据转移。

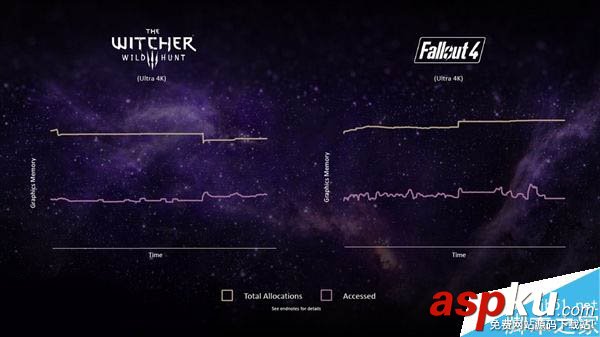

AMD还举了两个例子(是游戏而非专业应用),展示了《巫师3》、《辐射4》的显存占用情况,其中大约一半都被浪费了,也就是管理效率很低,而这正是Vega要解决的。

第二点,Vega拥有新的可编程几何流水线,每时钟周期峰值吞吐量翻了一番,可通过4个几何引擎处理最多11个三角形。

同时,Vega的几何引擎还加入了原语着色器(Primitive Shader),一个新的着色器阶段,和圆通的顶点、集合着色器引擎路径并行,可以高速抛弃隐藏的、没必要的原语。

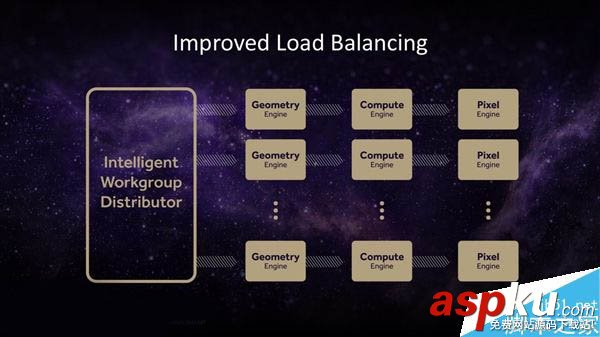

载入均衡也得到了改进,Vega通过智能工作组分配器,可以高效率地为计算引擎、几何引擎、像素引擎分派不同的任务负载。

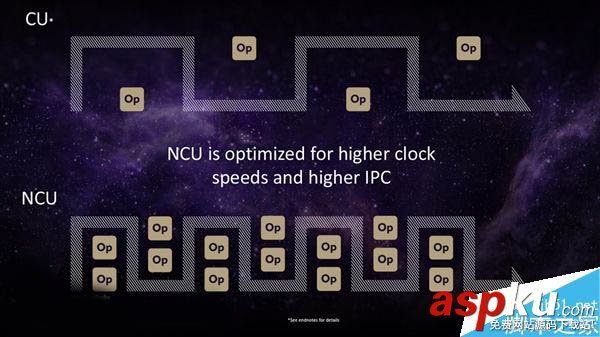

第三点,下一代计算引擎单元(NCU),这也是GCN架构引入以来最大规模的底层革新,每时钟周期可以处理512个8位或者256个16位或者128个32位操作,尤其是可以在单个FP32 ALU内处理一对FP16浮点操作,如果彼此兼容的话就可以打包到一起作为FP32进行处理,由此带动峰值吞吐能力翻番。

同时,寄存器还可以把一个FP32拆分成两个FP16,载入存储指令也可以转移FP16。

Vega仍然有64个ALU,FP32每时钟周期操作数128个也和GCN一样,但没有介绍具体是如何组织的。

Vega NCU同时针对高频率、高IPC都进行了优化,都有利于提升GPU综合性能。

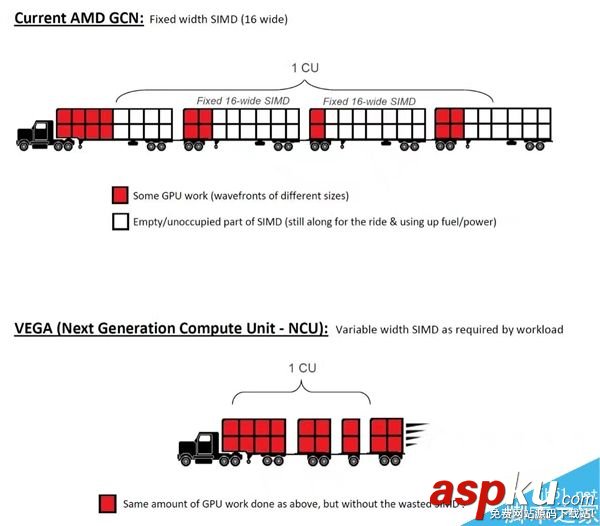

NCU还可以同时进行计算和图形处理,并且能够根据负载不同而变换SIMD单元宽度,结果就是以往需要多个计算单元才能完成的任务,现在只需一个就能搞定,不会造成浪费。

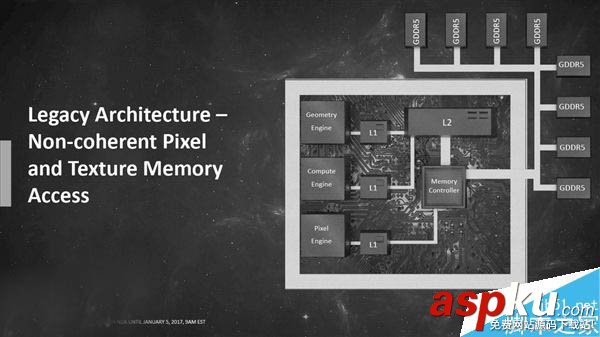

最后一点是下一代像素引擎,可以提出无效的渲染单元,在片上高速缓存内执行光栅化,同时打破了以往架构像素和纹理访问的不一致,实现硬件存储一致性,也就是各级缓存的数据都是最新的,二级缓存统一为渲染后端服务。

这就是Vega GPU初步披露的架构设计,重点就是革命性的高带宽缓存、新的可编程几何引擎、下一代计算单元、高级像素引擎。

至于更深入的底层架构设计,以及整体规格,以后再说。

新闻热点

疑难解答