对于FPGA、CPLD以及结构化ASIC设计,quartus ii是性能和效能首屈一指的设计软件。软件支持Altera名为Qsys的系统级集成工具新产品,实现了对Stratix® V FPGA系列的扩展支持,并且采用增强后的调试方案加快了电路板开发。本教程给出了如何用QuartusII,创建工程,创建源文件,综合编译,时序仿真,如何下载一系列的操作步骤。显示了一个完整的开发流程,供大家参考。

QuartusII创建工程:

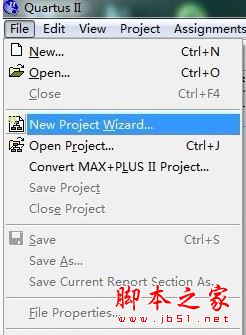

1.双击打开QuartusII软件,选择 file-----New Project Wizard...

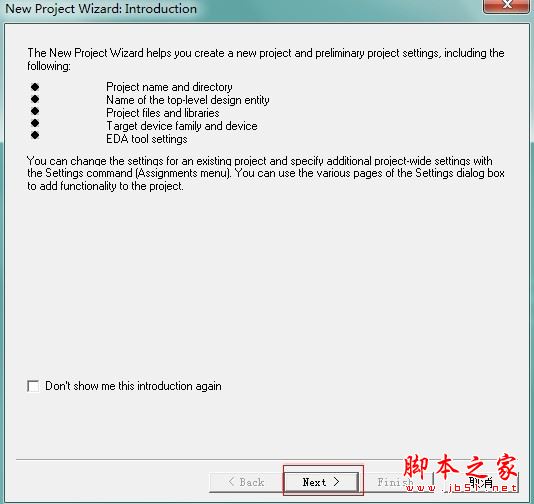

2.弹出如下窗口,本窗口介绍创建一个工程需要执行的设置,点击next。

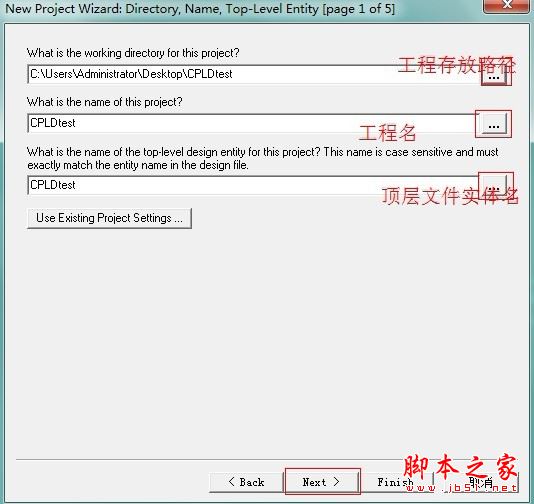

3.设置工程存放路径,工程名称,以及实体名,单击next

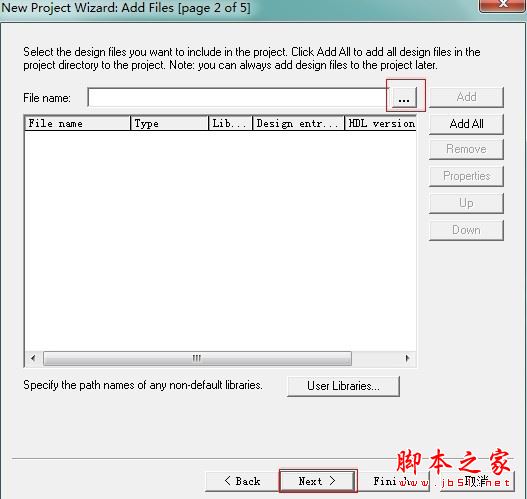

4.添加源文件到该工程,如果以及有源文件,浏览文件点击add,没有源文件,直接点击next

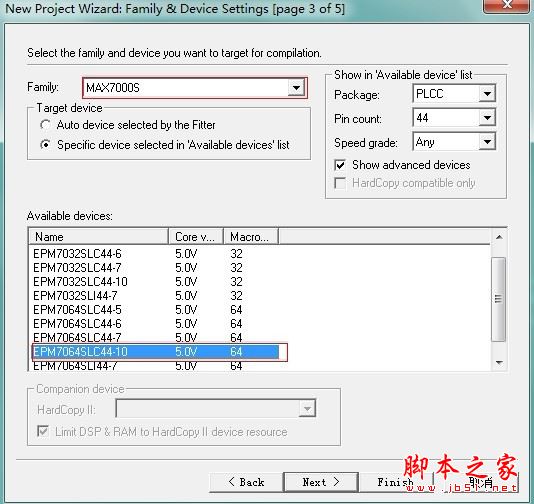

5.选择使用的芯片类型,系列,还有封装,管脚号,以及具体芯片的型号。然后next

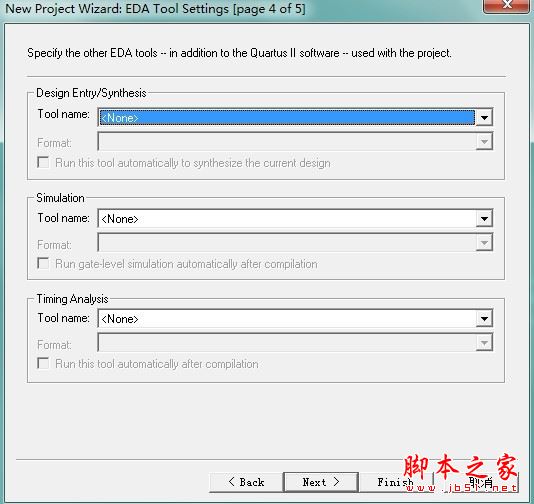

6.选择第三方工具,如果没有使用的,直接next

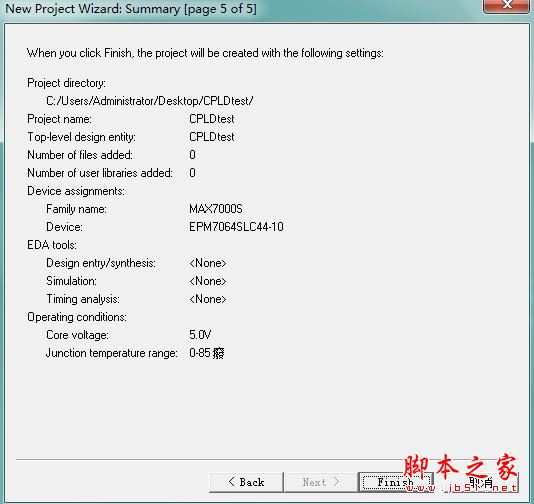

7.列出整个工程的概要,如果有设置错误,点击back重新设置,没有错误,点击finish

8.选择,file-----new,弹出如下窗口,再选择block diagram/Schematic File,点击OK

9.选择工具symbol tool

10.绘制原理图如下,这里只是演示操作,具体编程请查看相关书籍。该原理图方便验证,下载好程序,测量相应关管脚电压。看是否成功。

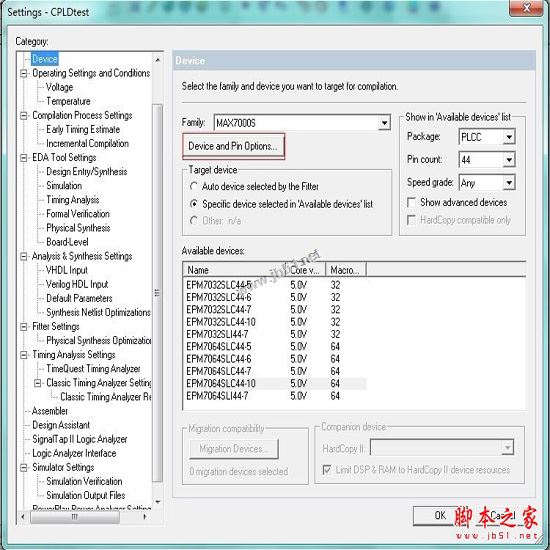

11.选择assignment-----setting,在编译前设置相关选项。

12. 选择device device and pin options.......

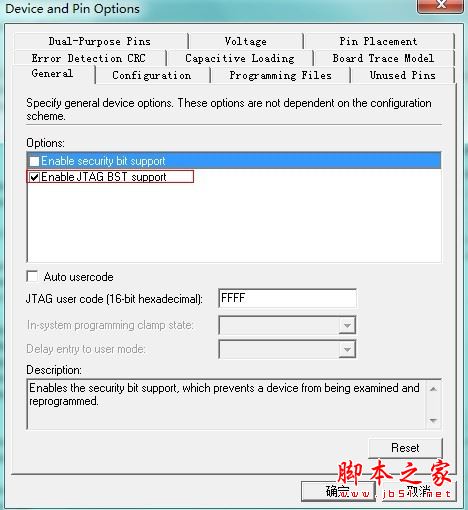

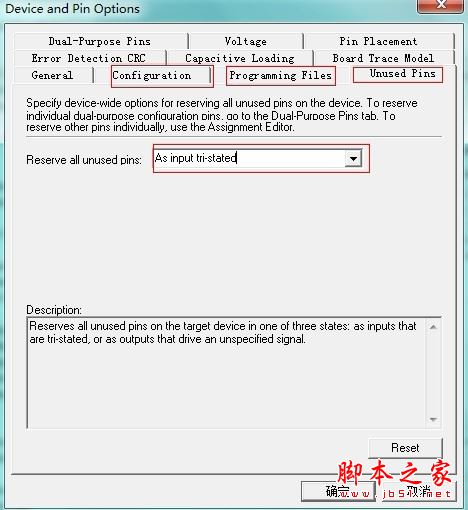

13.选择general 在options:中选择enable JTAG BST support

14.configuration里面,选择配置器件和编程方式,programming里面,选择输出产生下载文件格式,unused pins 里面选择闲置管脚状态。

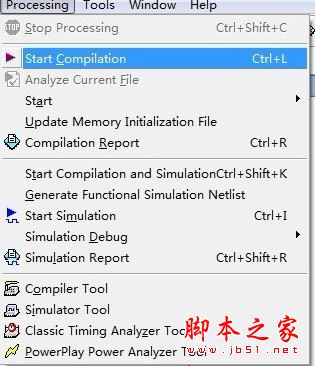

15.选择process-------start compilation,进行编译。

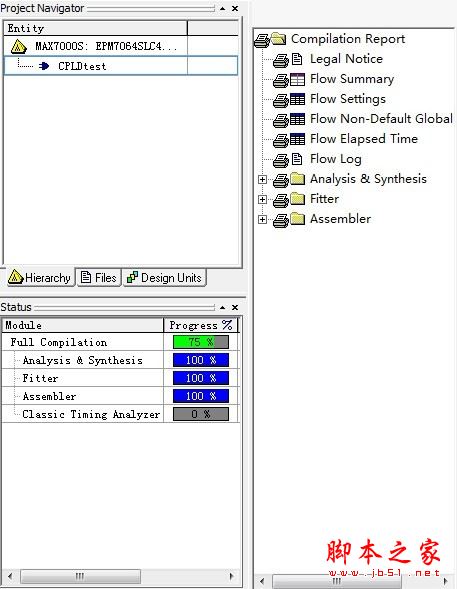

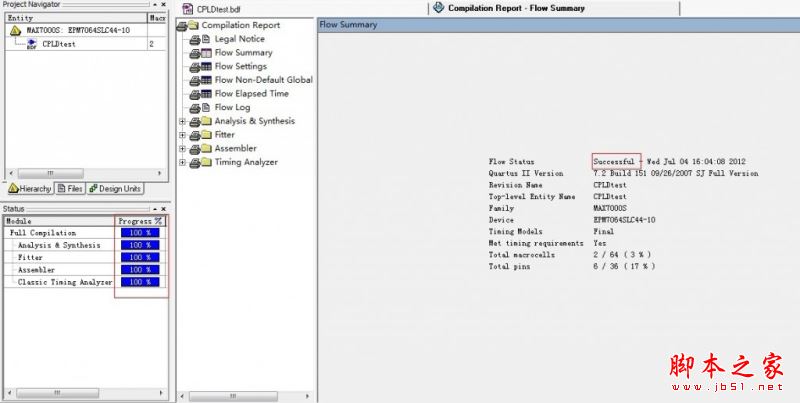

17,下图是编译过程显示的图片。

编译成功后,显示100%,flow summary窗口中,显示successful

以下步骤进行时序仿真

18.选择file-------new

点击other files,选择vector waveform file

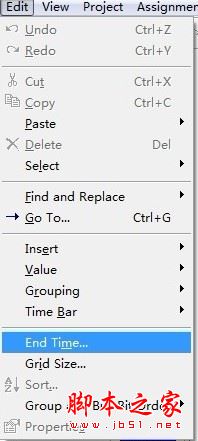

19.选择edit,endtime

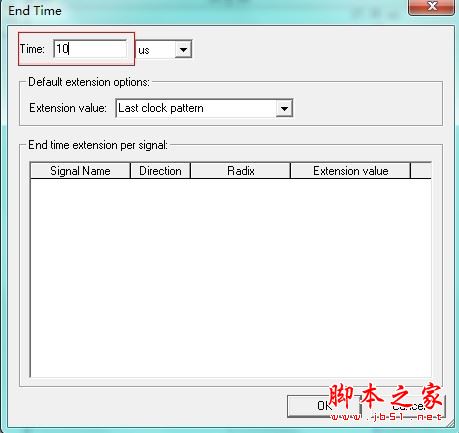

(此步骤十分重要)设置仿真时间

20.选择10us

21.保存波形文件,点击fie------save as ,保存文件名为CPLDtest.vmf

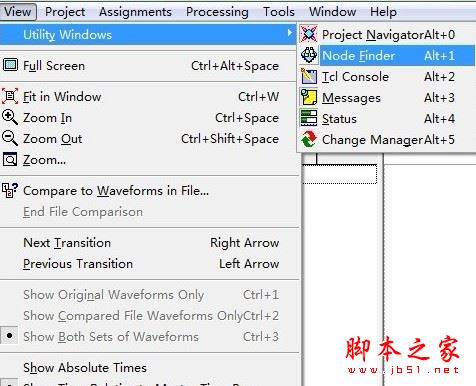

22.点击view-----utility windows------node finder

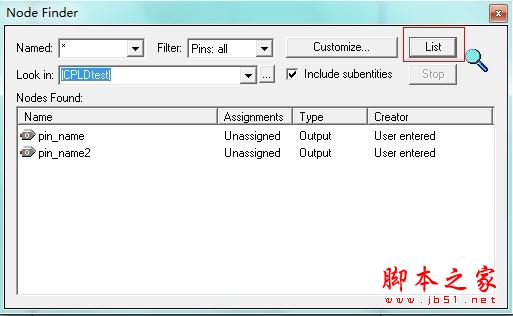

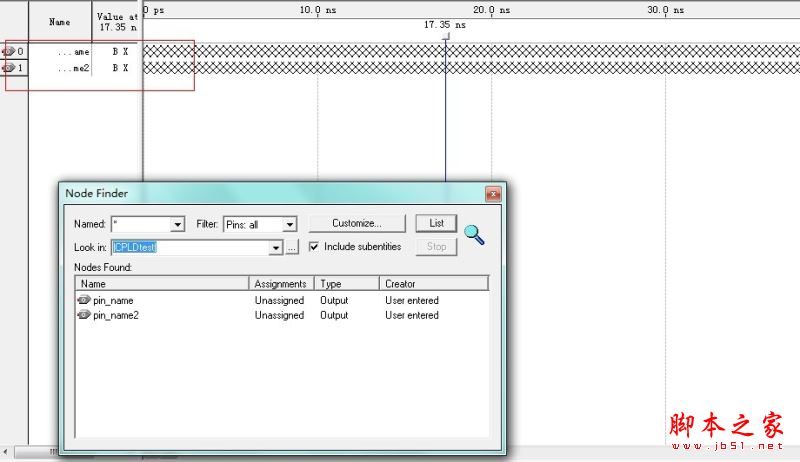

将端口信号添加到波形编辑器

23.点击list

24.拖动端口信号,到波形编辑器窗口

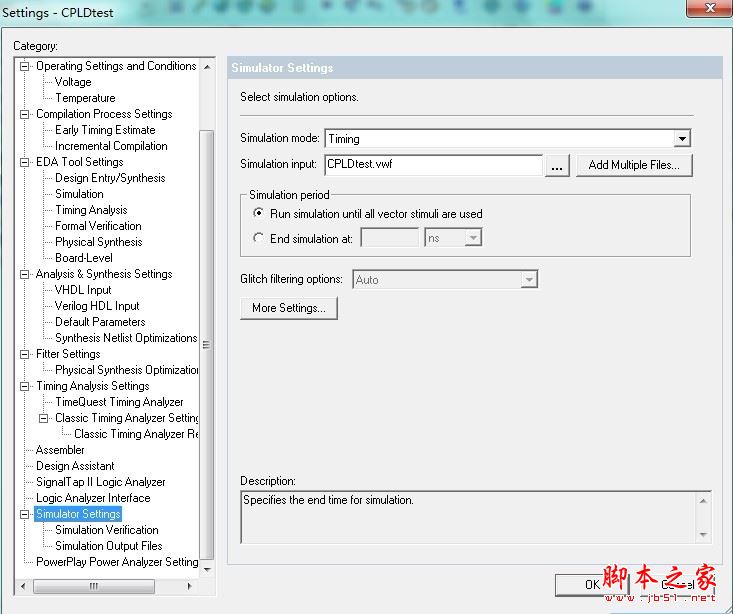

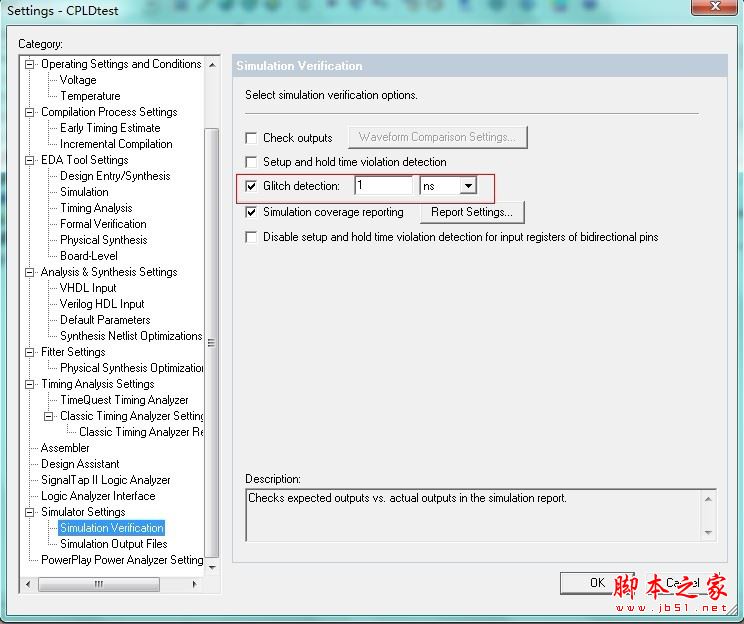

25.选择assignment----setting

点击simulation setting 选择波形仿真文件

单击simulating verification,选择毛刺检测glitch detection 1 ns

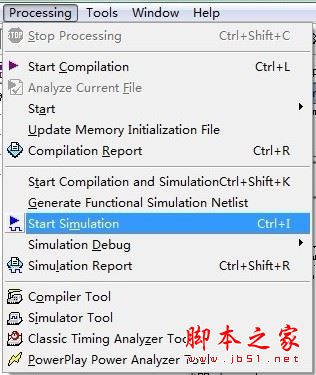

26.启动仿真,单击processin---start simulation

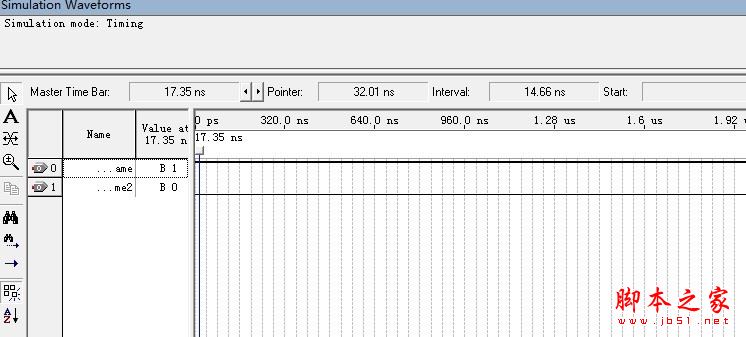

27.选择processing-----simulation report 观察仿真结果。

以下为下载设置

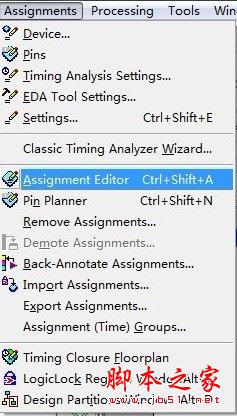

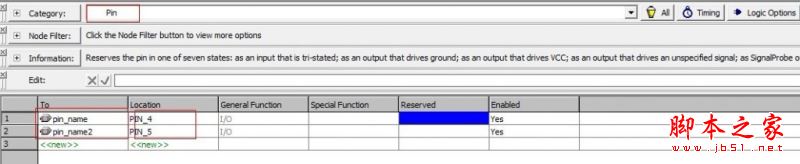

28.选择assignment---assignment editor

29.在category里面选择pin,

为端口号选择相应的管脚。选择4号5号管脚,下载成功的话,测量这两管脚应该一个高电平,一个低电平

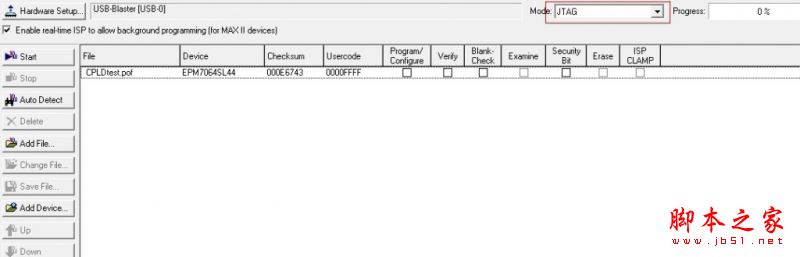

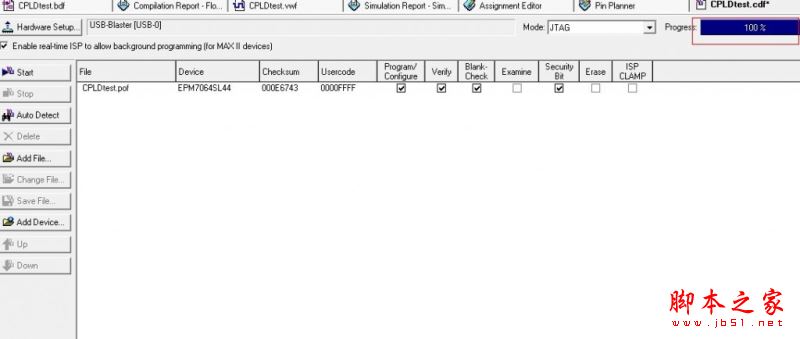

30.选择tool-----programmer

在mode中选择JTAG,如果没有出现下载文件,手动选择add file....选择CPLDtest.pof文件。

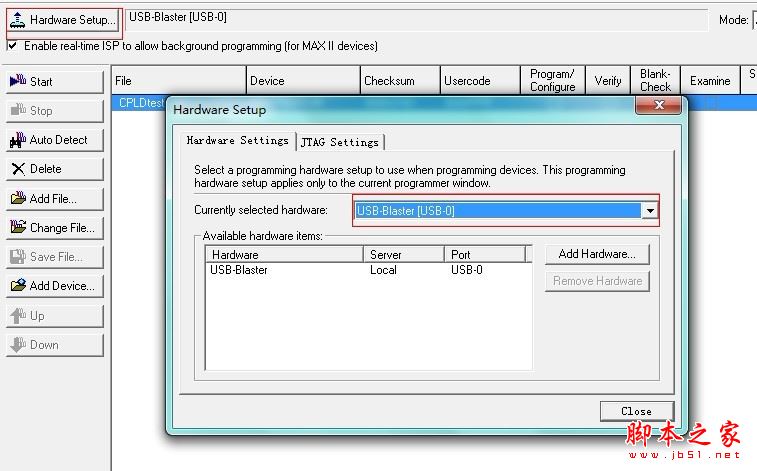

31 选择编程器

点击Hadware Setup..弹出对话框中选择,usb blaster,单击close

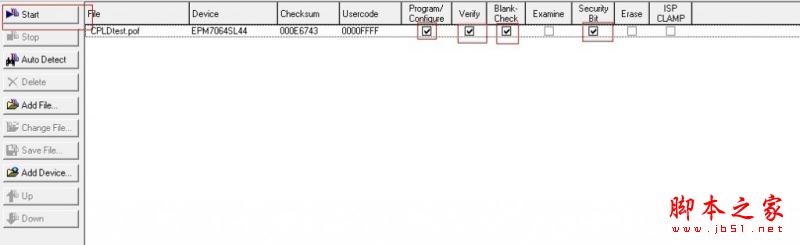

32.勾选相应配置选项,单击start开始下载程序

33.进度条都100%时说明下载完成。0%到100%,本次下载用了25秒钟,如果进度条很快几秒钟就到100%说明没成功下载。最后,万用表测量芯片管脚(4号高电平,5号低电平)。验证程序确实下载OK

以上就是对quartus怎么用以及Quartus II创建工程及编译过程的使用方法全部内容的介绍,更多内容请继续关注武林网网站!

新闻热点

疑难解答

图片精选